# **INSTRUCCIONES**

Las instrucciones del microcontrolador Z8<sup>PLUS</sup> se pueden clasificar en grupos de acuerdo a su función como:

- Instrucciones de carga

- Manipulación de bit

- Aritméticas

- Transferencias

- Lógicas

- Rotación y desplazamiento

- Control de programa

- Control de CPU

Cuando las instrucciones son ejecutadas, los registros definidos como fuentes son de solo lectura. Todos los registros de propósito general funcionan como:

- Acumuladores

- Apuntadores de dirección

- Registros índice

- Áreas de stack

Las siguientes tablas nos muestran las instrucciones que pertenecen a cada grupo y el numero de operandos que se requiere para cada una. El operando fuente es "scr", el operando destino "dst" y las condiciones de código, "cc".

Tabla 9-1 Instrucciones de carga

| Mnemonic | Operands | Instruction   |

|----------|----------|---------------|

| CLR      | dst      | Clear         |

| LD       | dst, src | Load          |

| LDC      | dst, src | Load Constant |

| POP      | dst      | Pop           |

| PUSH     | src      | Push          |

Tabla 9-2 Instrucciones de operaciones aritméticas

| Mnemonic | Operands | Instruction         |

|----------|----------|---------------------|

| ADC      | dst, src | Add with Carry      |

| ADD      | dst, src | Add                 |

| СР       | dst, src | Compare             |

| DA       | dst      | Decimal Adjust      |

| DEC      | dst      | Decrement           |

| DECW     | dst      | Decrement Word      |

| INC      | dst      | Increment           |

| INCW     | dst      | Increment Word      |

| SBC      | dst, src | Subtract with Carry |

| SUB      | dst, src | Subtract            |

Tabla 9-3 Instrucciones de operaciones lógicas

| Mnemonic | Operands | Instruction          |

|----------|----------|----------------------|

| AND      | dst, src | Logical AND          |

| СОМ      | dst      | Complement           |

| OR       | dst, src | Logical OR           |

| XOR      | dst, src | Logical Exclusive OR |

Tabla 9-4 Instrucciones de control de programa

| Mnemonic | Operands | Instruction                 |

|----------|----------|-----------------------------|

| CALL     | dst      | Call Procedure              |

| DJNZ     | dst, src | Decrement and Jump Non-Zero |

| IRET     |          | Interrupt Return            |

| JP       | cc, dst  | Jump                        |

| JR       | cc, dst  | Jump Relative               |

| RET      |          | Return                      |

Tabla 9-5 Instrucciones de manipulación de bits

| Mnemonic | Operands | Instruction                   |

|----------|----------|-------------------------------|

| TCM      | dst, src | Test Complement<br>Under Mask |

| TM       | dst, src | Test Under Mask               |

| AND      | dst, src | Bit Clear                     |

| OR       | dst, src | Bit Set                       |

| XOR      | dst, src | Bit Complement                |

Tabla 9-6 Instrucciones de carga

| Mnemonic Operands Instruction |          | Instruction                     |

|-------------------------------|----------|---------------------------------|

| LDCI                          | dst, src | Load Constant<br>Auto Increment |

Tabla 9-7 Instrucciones de rotación y desplazamiento

| Mnemonic | Operands | Instruction                |

|----------|----------|----------------------------|

| RL       | dst      | Rotate Left                |

| RLC      | dst      | Rotate Left Through Carry  |

| RR       | dst      | Rotate Right               |

| RRC      | dst      | Rotate Right Through Carry |

| SRA      | dst      | Shift Right Arithmetic     |

| SWAP     | dst      | Swap Nibbles               |

Tabla 9-8 Instrucciones de control del CPU

| Mnemonic | Operands | Instruction           |

|----------|----------|-----------------------|

| CCF      |          | Complement Carry Flag |

| Dl       |          | Disable Interrupts    |

| EI       |          | Enable Interrupts     |

| HALT     |          | Halt                  |

| NOP      |          | No Operation          |

| RCF      |          | Reset Carry Flag      |

| SCF      |          | Set Carry Flag        |

| SRP      | src      | Set Register Pointer  |

| STOP     |          | Stop                  |

| WDT      |          | Refresh WDT           |

#### **BANDERAS**

El Registro de banderas es el que informa al usuario el estado actual del microcontrolador. Las banderas y la posición de sus bits en el registro de banderas (Flag Register) se muestran en la figura.

El Registro de banderas contiene 8 bits que nos dicen el estado del microcontrolador y son manipuladas por las operaciones del CPU. Cuatro de estos bits (C, V, Z y S) se pueden examinar para usar las condiciones de salto condicional. Dos banderas (H y D) son usadas para aritmética BCD. Los otros dos bits en el registro de banderas son para las banderas del reinicio por termino de conteo del WDT y para la bandera del Stop Mode Recovery.

Como en cualquier otro registro de instrucciones, los bits de este registro se pueden poner en estado alto o bajo por medio de instrucciones; sin embargo, solo se pueden usar instrucciones que no afecten el registro de banderas como consecuencia de su ejecución.

| Bit   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-----|-----|-----|-----|-----|-----|-----|

| R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | U   | U   | U   | U   | U   | U   | *   | *   |

Fig. 9.1 Registro de banderas

### **BANDERA DE ACARREO (C)**

La bandera de acarreo se pone en estado alto cuando el resultado de una operación aritmética genera un acarreo o un préstamo del bit 7. De lo contrario, la bandera de acarreo se pone en estado bajo. En las instrucciones de rotación y desplazamiento, la bandera de acarreo contiene el ultimo valor del bit que sale del registro en el que se hace la operación.

Una instrucción puede poner en estado alto, en estado bajo o complementar la bandera de acarreo.

La bandera de acarreo no se ve afectada por el RESET.

## **BANDERA DE CERO (Z)**

Para operaciones lógicas y aritméticas, la bandera de cero se pone en estado alto si el resultado es cero. En caso contrario la bandera se mantiene en estado bajo.

Si el resultado de examinar un bit de un registro es cero entonces la bandera de cero se pone en estado alto. En caso contrario la bandera se mantiene en estado bajo. Si el resultado de la operación de rotación o desplazamiento es cero entonces la bandera de cero se pone en estado alto.

La bandera de cero no se ve afectada por el comando de RESET.

### **BANDERA DE SIGNO (S)**

La bandera de signo guarda el bit mas significativo del resultado de una operación lógica, aritmética, de rotación o de desplazamiento.

Cuando se llevan a cabo operaciones aritméticas con números que tienen signos, la notación binaria de complemento a dos es utilizada para representar y procesar información. Un numero positivo se identifica con un cero en el bit más significativo, por lo tanto, en este caso la bandera de signo también es cero.

Un número negativo es identificado con un 1 en el bit mas significativo, por lo tanto la bandera de signo también es 1.

La bandera de cero no se ve afectada por el RESET.

## **BANDERA DE SOBREFLUJO (V)**

Para operaciones aritméticas de rotación o de desplazamiento, la bandera de sobreflujo se pone en estado alto cuando el resultado es más grande que el máximo número posible (mayor de 127) o menor que el numero mínimo posible (menor que –128) que puede ser representado en la forma de complemento a dos. La bandera de sobreflujo se mantiene en estado bajo si no ocurren sobreflujos.

La bandera de sobreflujo no se ve afectada por el RESET.

### **BANDERA DE AJUSTE DECIMAL (D)**

La bandera de ajuste decimal es usada en aritmética decimal. Desde que el algoritmo para operaciones BCD es diferente para la suma y la resta, esta bandera especifica que tipo de instrucción fue la última que se ejecuto para que la siguiente operación pueda funcionar apropiadamente. El usuario no puede tener acceso a esta bandera.

Después de una resta, esta bandera se pone en estado alto y después de una suma se pone en estado bajo.

Esta bandera no se ve afectada por el RESET.

### **BANDERA DE MEDIO ACARREO (H)**

La bandera de medio acarreo se pone en estado alto cuando una suma genera un acarreo en el bit 3 o cuando una resta genera un "préstamo " del bit 3. Esta bandera de medio acarreo es usada en las operaciones de ajuste decimal para convertir un resultado binario de una suma o una resta en un resultado decimal (BCD). Al igual que en la bandera de ajuste decimal el usuario no puede tener acceso a esta bandera.

Esta bandera no se ve afectada por el RESET.

#### BANDERA DEL WATCH DOG TIMER (WDT)

La bandera de Watch Dog Timer se activa cuando el tiempo del Watch Dog Timer llega a cero y ocurre un reset. Esto le permite al software determinar cuando ha terminado el conteo del WDT.

Esta bandera se vuelve a poner en estado bajo con el pin del reset. Las banderas WDT y SMR son las únicas que se ven afectadas por el RESET. Este comportamiento le permite al software determinar cuando ha ocurrido un RESET, si el tiempo de conteo del WDT ha terminado, o si ha ocurrido un regreso del modo STOP.

El software debe de "limpiar" esta bandera después de detectar esta condición. En caso contrario podría haber un comportamiento inesperado.

## BANDERA DE RECUPERACIÓN DE MODO STOP (SMR)

La bandera de Recuperación del Modo Stop (Stop Mode Recovery, SMR) se pone en estado alto con la ejecución del modo STOP. Esto permite al software

determinar si un retorno del modo STOP ha ocurrido para regresar al estado activo.

Esta bandera se limpia con el pin de RESET. Las banderas WDT y SMR son las únicas banderas que se ven afectadas por el RESET. Este comportamiento permite al software determinar cuando ha ocurrido un RESET, si el tiempo del WDT ha terminado, o si un regreso del modo STOP ha ocurrido.

El programa debe de limpiar esta bandera después de detectar esta condición. En caso contrario podría haber un comportamiento inesperado.

Tabla 9-9 Definiciones de configuración de banderas

| Symbol | Definition                            |  |

|--------|---------------------------------------|--|

| 0      | Cleared to 0                          |  |

| 1      | Set to 1                              |  |

|        | Set or cleared according to operation |  |

| -      | Unaffected                            |  |

| X      | Undefined                             |  |

Tabla 9-10 Códigos de condición

| Binary | HEX | Mnemonic | Definition   | Flag Settings |

|--------|-----|----------|--------------|---------------|

| 0000   | 0   | F        | Always False | -             |

| 1000   | 8   | (blank)  | Always True  | -             |

| 0111   | 7   | С        | Carry        | C=1           |

| 1111   | F   | NC       | No Carry     | C-0           |

| 0110   | 6   | Z        | Zero         | Z=1           |

| 1110   | E   | NZ       | Non-Zero     | Z = 0         |

| 1101   | D   | PL       | Plus         | S = 0         |

| 0101   | .5  | MI       | Minus        | S = 1         |

| 0100   | 4   | ov       | Overflow     | V = 1         |

| 1100   | С   | NOV      | No Overflow  | V = 0         |

Las banderas C, Z, S y V controlan la operación de las instrucciones de salto condicional. Las condiciones de código se ven resumidas en la tabla 8-10.

## **NOTACIÓN Y CODIFICACIÓN BINARIA**

Los operandos y los estados de banderas usan una notación. Las notaciones de los operandos, condiciones de código y modos de direccionamiento se describen en la tabla 8-11.

Tabla 9-11 Abreviaciones

| Notation | Address Mode                                          | Operand      | Range*                                                                                                                           |

|----------|-------------------------------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------|

| cc       | Condition Code                                        |              | See Table 3-11, condition codes                                                                                                  |

| r        | Working Register                                      | Rn           | n = 0 - 15                                                                                                                       |

| R        | Register<br>or<br>Working Register                    | Reg<br>Rn    | Reg. represents a number in the range of 00H to FFH $n = 0 - 15$                                                                 |

| RR       | Indirect Register Pair<br>or<br>Working Register Pair | Reg<br>RRp   | p = 0, 2, 4, 6, 8, 10, 12, or 14                                                                                                 |

| Ir       | Indirect Working Register                             | @Rn          | n=0 -15                                                                                                                          |

| IR       |                                                       |              | Reg. represents a number in the range of<br>00H to FFH<br>n = 0-15                                                               |

| Irr      | Indirect Working Register<br>Pair                     | @RRp         | p=0, 2, 4, 6, 8, 10, 12, or 14                                                                                                   |

| IRR      | Indirect Register Pair<br>or<br>Working Register Pair | @Reg<br>@RRp | Reg. represents an even number in the<br>range 00H to FFH<br>p=0, 2, 4, 6, 8, 10, 12, or 14                                      |

| х        |                                                       |              | Reg. represents a number in the range of 00H to FFH $n = 0 - 15$                                                                 |

| DA       | Direct Address                                        | Addrs        | Addrs. represents a number in the range of 0000H to FFFFH                                                                        |

| RA       | RA Relative Address                                   |              | Addrs. represents a number in the range<br>of +127 to -128 which is an offset relative<br>to the address of the next instruction |

| IM       | Immediate                                             | #Data        | Data is a number between 00H to FFH                                                                                              |

<sup>\*</sup>See the device product specification to determine the exact register file range available. The register file size varies by the device type.

La siguiente tabla nos muestra símbolos adicionales:

Tabla 9-12 símbolos adicionales

| Symbol | Definition                    |

|--------|-------------------------------|

| dst    | Destination Operand           |

| src    | Source Operand                |

| @      | Indirect Address Prefix       |

| SP     | Stack Pointer                 |

| PC     | Program Counter               |

| FLAGS  | Flag Register (FCH)           |

| RP     | Register Pointer (FDH)        |

| IMR    | Interrupt Mask Register (FBH) |

| #      | Immediate Operand Prefix      |

| %      | Hexadecimal Number Prefix     |

| Н      | Hexadecimal Number Suffix     |

| В      | Binary Number Suffix          |

| OPC    | op code                       |

La asignación de un valor se indica con el símbolo ←, por ejemplo:

indica que el dato destino se suma al dato fuente y el resultado se guarda en la localidad del destino.

La notación addr (n) se usa para hacer referencia a un bit "n" de una localidad dada. El siguiente ejemplo hace referencia al bit 7 del operando destino:

dst (7)

Tabla 9-13 Resumen de instrucciones

| Instruction and Operation            | Address<br>Mode |     | op code    | Flags Affected |    |    |      |    |    |  |

|--------------------------------------|-----------------|-----|------------|----------------|----|----|------|----|----|--|

|                                      | dst             | src | Byte (Hex) | С              | Z  | s  | ٧    | D  | н  |  |

| ADC dst, src<br>dst ← dst + src +C   | †               |     | 1[]        | •              | *  | •  | •    | 0  |    |  |

| ADD dst, src<br>dst ← dst + src      | t               |     | 0[ ]       | ٠              | *  | *  | ٠    | 0  |    |  |

| AND dst, src<br>dst ← dst AND src    | t               |     | 5[ ]       | Ŧ              | *  | *  | 0    | -  | -  |  |

| CALL src<br>SP ← SP − 2<br>PC ← src  |                 | DA  | D6         | 5              | -  | -  | -    | -  | 2  |  |

| CALL src<br>SP ← SP – 2<br>PC ← @src |                 | IRR | D4         | 2              | -  | 20 | -    | 82 | 2  |  |

| CCF<br>C ←NOT C                      |                 |     | EF         | •              | 12 | -  | 0.10 | -  | -  |  |

| CLR dst<br>dst ← 0                   | R<br>IR         |     | B0<br>B1   | +              | æ  | -  | 8    | -  | -  |  |

| COM dst<br>dst ← NOT dst             | R<br>IR         |     | 60<br>61   | 23             |    | *  | 0    |    | -  |  |

| CP dst, src<br>dst – src             | Ť               |     | A[ ]       | •              |    |    |      | -  | =  |  |

| DA dst<br>dst ← DA dst               | R<br>IR         |     | 40<br>41   | *              |    | ٠  |      | 55 | -  |  |

| DEC dst<br>dst ← dst – 1             | R<br>IR         |     | 00<br>01   | +              | ,  | *  | •    | -  | 1- |  |

| DECW dst<br>dst ← dst − 1            | RR<br>IR        |     | 80<br>81   | 7              |    | ٠  |      | -  | -  |  |

Tabla 9-13 (continuación) resumen de instrucciones

| Instruction and Occupies                                                                                                                     | Address Mode |     | op code                   | Flags Affected |   |              |     |   |     |  |

|----------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----|---------------------------|----------------|---|--------------|-----|---|-----|--|

| Instruction and Operation                                                                                                                    | dst          | SFC | Byte (Hex)                | С              | Z | S            | V   | D | Н   |  |

| DI<br>$IMR(7) \leftarrow 0$                                                                                                                  |              |     | 8F                        |                | + | +            | -   | - | -   |  |

| DJNZ, dst, src r RA<br>dst $\leftarrow$ dst $-1$<br>if dst $\neq$ 0<br>then PC $\leftarrow$ PC + src<br>Range: $-128 \le \text{src} \le 127$ | RA           |     | rA<br>(r = 0 - F)         | 2              | - | -            |     |   |     |  |

| EI<br>IMR(7) ← 1                                                                                                                             |              |     | 9F                        | E              | - | +            | -   | - | -   |  |

| HALT                                                                                                                                         |              |     | 7F                        | -              | - | -            | -   | - | -   |  |

| INC dst dst $\leftarrow$ dst + 1                                                                                                             | r<br>R<br>IR |     | rE<br>(r=0-F)<br>20<br>21 | 9              |   | *            | *   | - | -   |  |

| INCW dst<br>dst ← dst + 1                                                                                                                    | RR<br>IR     |     | A0<br>A1                  | æ              |   |              | *   | - | -   |  |

| IRET<br>FLAGS←@SP;<br>SP ← SP + 1<br>PC ← @SP;<br>SP ← SP + 2;<br>IMR(7) ← 1                                                                 |              | -   | BF                        | •              |   | •            | •   | • | •   |  |

| JP cc, src<br>if cc is true,<br>then PC ← src                                                                                                |              | DA  | ceD<br>(cc = 0 - F)       | -              | - | -            | -   | - | -   |  |

| JP src<br>PC ← @src                                                                                                                          |              | IRR | 30                        | -              | - | -            | 77. | - | -   |  |

| JR cc, src<br>if cc is true,<br>then PC ← PC + src<br>Range: -128 ≤ src ≤ 127                                                                |              | RA  | ccB<br>c = 0 - F          | _              | - | C <u>E</u> X | 2   | - | 172 |  |

Tabla 9-13 (continuación) resumen de instrucciones

| Г                                   | Address Mode |     | op code     | Flags Affected |     |   |   |   |   |  |

|-------------------------------------|--------------|-----|-------------|----------------|-----|---|---|---|---|--|

| Instruction and Operation           | dst          | src | Byte (Hex)  | C              | Z   | S | V | D | Н |  |

| LD dst, src                         | r            | Im  | r C         | _              |     | - |   |   | - |  |

| $dst \leftarrow src$                | r            | R   | r 8         |                |     |   |   |   |   |  |

|                                     | R            | r   | г9          |                |     |   |   |   |   |  |

|                                     |              |     | (r = 0 - F) |                |     |   |   |   |   |  |

|                                     | r            | X   | C7          |                |     |   |   |   |   |  |

|                                     | X            | r   | D7          |                |     |   |   |   |   |  |

|                                     | Ĭ.           | Ir  | E3          |                |     |   |   |   |   |  |

|                                     | Ir           | r   | F3          |                |     |   |   |   |   |  |

|                                     | R            | R   | E4          |                |     |   |   |   |   |  |

|                                     | R            | IR  | E5          |                | ,   |   |   |   |   |  |

|                                     | R            | IM  | E6          |                |     |   |   |   |   |  |

|                                     | IR           | IM  | E7          |                |     |   |   |   |   |  |

|                                     | IR           | R   | F5          |                |     |   |   |   |   |  |

| LDC dst, src                        | r            | Irr | C2          | _              | _ " | _ | _ | _ | _ |  |

| dst ← src                           | lrr          | r   | D2          |                |     |   |   |   |   |  |

| LDCI dst, sre                       | Ir           | Irr | C3          |                |     | _ | _ |   | _ |  |

| @dst ← @src                         | lrr          | r   | D3          |                |     |   |   |   |   |  |

| $dst \leftarrow dst + 1$            |              |     |             |                |     |   |   |   |   |  |

| src ←src + 1                        |              |     |             |                |     |   |   |   |   |  |

| NOP                                 |              |     | FF          | _              | _   |   | _ | _ | _ |  |

| OR dst, src                         | †            |     | 4[]         |                | *   | * | 0 |   | _ |  |

| $dst \leftarrow dst OR src$         |              |     |             |                |     |   |   |   |   |  |

| POP dst                             | R            |     | 50          |                | _   | _ | _ | _ | _ |  |

| dst ← @SP                           | IR           |     | 51          |                |     |   |   |   |   |  |

| $SP \leftarrow SP + 1$              |              |     |             |                |     |   |   |   |   |  |

| PUSH src                            | R            |     | 70          | _              |     |   | _ | _ | _ |  |

| SP ← SP – 1                         | IR           |     | 71          |                |     |   |   |   |   |  |

| @SP ← src                           |              |     |             |                |     |   |   | ! |   |  |

| RCF                                 |              |     | CF          | 0              | _   | _ | - | _ | _ |  |

| C ← 0                               |              |     |             |                |     |   |   |   |   |  |

| RET                                 |              |     | AF          | _              | _   | - | _ | _ | _ |  |

| PC ← @\$P;                          |              |     |             |                |     |   |   |   |   |  |

| $SP \leftarrow SP + 2$              |              |     |             |                |     |   |   |   |   |  |

| RL dst                              | R            |     | 90          | *              | *   | * | * | - | _ |  |

| C 7 0 4                             | IR.          |     | 91          |                |     |   |   |   |   |  |

| [C] <del>-</del> 7, 0] <del>-</del> |              |     |             |                |     | L | L | l |   |  |

Tabla 9-13 (continuación) resumen de instrucciones

|                                                | Addres  | s Mode | op code    | Flags Affected |   |   |   |   |   |  |

|------------------------------------------------|---------|--------|------------|----------------|---|---|---|---|---|--|

| Instruction and Operation                      | dst     | STC    | Byte (Hex) | Ç              | Z | S | ٧ | D | Н |  |

| RLC dst                                        | R<br>IR |        | 10<br>11   | *              | * | * | * | _ | _ |  |

| RR dst<br>□□□  □  □  □  □  □  □  □  □  □  □  □ | R<br>IR |        | E0<br>EI   | *              | * | * | * | _ | _ |  |

| RRC dst                                        | R<br>IR |        | C0<br>C1   | *              | * | * | * | - |   |  |

| SBC dst, src<br>dst ← dst – src –<br>C         | †       |        | 3[]        | *              | * | * | * | 1 | * |  |

| SCF<br>C ← 1                                   |         |        | DF         | 1              | _ | _ | - | _ | - |  |

| SRA dst                                        | R<br>IR |        | D0<br>D1   | *              | * | * | 0 | _ | _ |  |

| <b>SRP</b> src $RP \leftarrow src$             | lm      |        | 31         | _              | _ | _ | - |   | _ |  |

| STOP                                           |         |        | 6F         | _              |   | _ |   | _ | _ |  |

| SUB dst, src<br>dst ← dst – src                | †       |        | 2[ ]       | *              | * | * | * | 1 | * |  |

| SWAP dst 7 4[3 0                               | R<br>IR |        | F0<br>FI   | _              | * | * |   | _ | _ |  |

| TCM dst, src<br>(NOT dst) AND src              | †       |        | 6[]        | _              | * | * | 0 | _ | - |  |

| TM dst, sre<br>dst AND sre                     | †       |        | 7[]        |                | * | * | 0 | _ | _ |  |

| WDT                                            |         |        | 5F         | _              |   | _ | _ | _ | - |  |

| XOR dst, src<br>dst ← dst XOR src              | †       |        | 7[]        | _              | * | * | 0 | _ | _ |  |

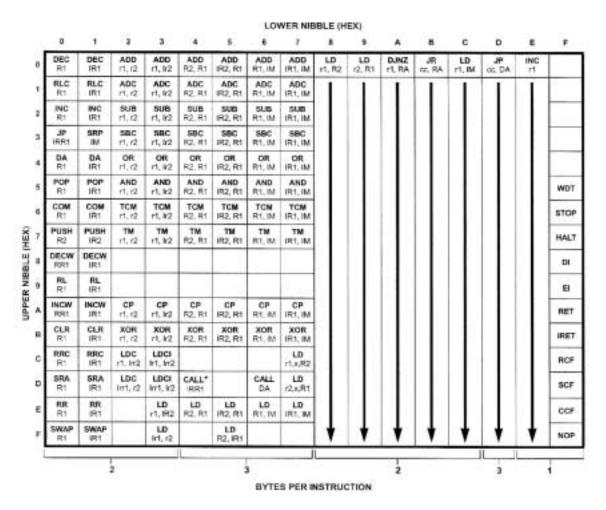

Fig. 9.2 Mapa de códigos